im电竞官网平台·关于光纤通信的ESD保护

发布时间:2024-05-19 11:15:17 来源:im电竞官网

作者:IM电竞官网注册 点击次数:16次

通常被用于长距离通信(50公里以上),但这些高端在全球范围内的需求量是非常有限的。最近,那些运营大数据(Facebook、谷歌、Amazon等)正在替换服务器之间的传统铜线连接方式。基于铜连接的方法被认为是提升数据传输能力的瓶颈,而光通信则可以显著增加服务器之间的带宽,降低系统复杂性、功耗以及成本。

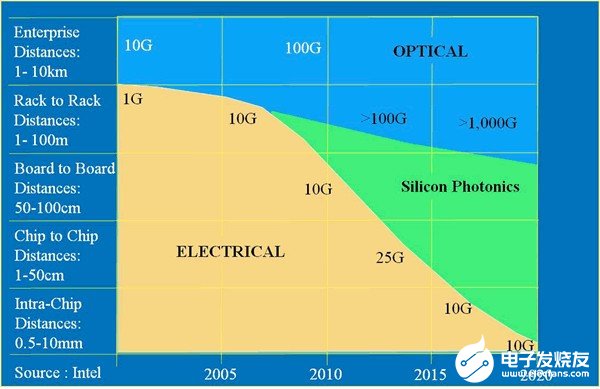

英特尔光通信团队的工程师总结了硅光子技术在不同接口距离上的潜力。传统的光通信将主要用于长距离通信。由于低功耗、低成本和高带宽的结合,硅光子将在更短的距离内取代电通信。

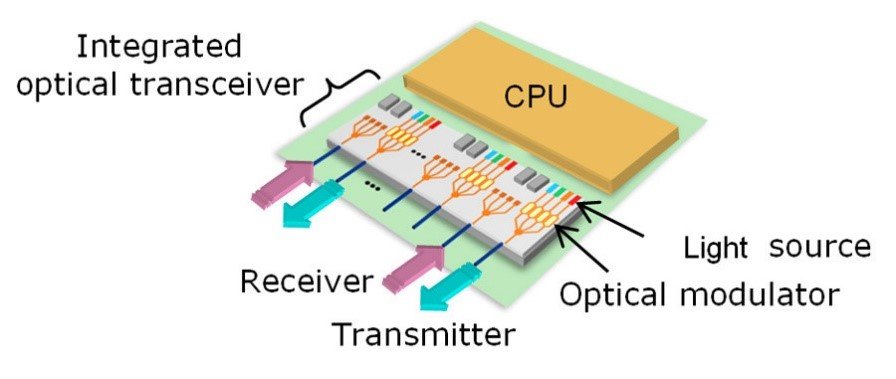

因此,光互连供应商现在需要生产大量的产品以应对以上需求。为了降低成本,他们将光学部件(激光二极管)与数字控制电路分开。对于来说,常规的CMOS工艺可以用于大规模生产。同时在过去的十年里随着多项技术的突破,传统的CMOS工艺现在已经可以用来制造各种光学元件,如波分复用器(WDM)、激光器、探测器、波导(例如SOI工艺)。

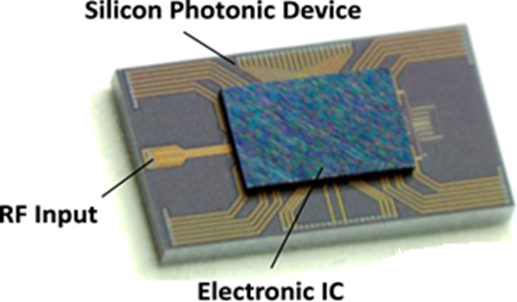

通过先进封装技术,比如2.5D(electronicinterposer)和3D(flip-chip)集成,可以把光电器件封装在一个IC中使用。混合集成允许设计人员为每个功能选择最佳的工艺选项。例如,数字功能可以集成在高性能、小尺寸的高端CMOS工艺技术中。但光子芯片无法从这种最小的特征尺寸中受益因此可以采用更加成熟的SOI技术进行设计,从而显着降低了总成本。

用于控制光学部件和在收发后处理信号的集成电路是使用先进的CMOS技术(如28nm)制造的。接口由高速(25Gbps或更高)SerDes型电路组成。设计者利用薄氧化物晶体管来制造这种的高速差分电路。然而,这些晶体管却非常敏感,很容易在静电放电(ESD)等瞬态事件中被损坏。因为这些晶体管在瞬态过程中能承受的最大电压不超过4V。

尽管敏感的PAD并未连接到封装的外部,但它们在组装过程中仍可能受到ESD应力。因此需要在PAD处插入足够的多保护钳位。另一方面,对于信号完整性来说,限制PAD和电源线之间的电容同样很重要。多位学者已经在研究中选择了具有低寄生电容的片上ESD保护方法。比如基于二极管或SCR保护的概念已用于RC芯片[2-6]。然而,对于那些在低电压下运行的最敏感的接口来说,I/O上基于双二极管结合一个(分布式的)电源钳位ESD保护并不一定有效[6]。

许多先进的CMOS晶圆代工厂提供了整套的I/O和ESD保护电路。然而,这些标准的、通用的接口块并不适合硅光芯片的设计。

—高速接口通常在低于标准I/O电压水平下工作(与I/O电路的1.8V、2.5V或3.3V相比,1.0V或更低)

—高速SerDes电路不能承受信号路径上增加的大量寄生电容或电阻。一个典型的模拟I/O将引入150fF的寄生电容,远远高于电路所能容忍的范围。

在过去的10年里,多家硅光子产品设计公司已经联系Sofics并寻求技术支持。在这些项目中,我们着重于保护晶片上的高速接口(Tx,Rx)以及低电压压PAD。

对于1.8V的常规低速I/Os, 晶圆代工厂提供的模拟/数字I/O库就足够了。这些PAD的ESD要求为2kV HBM。但另一方面,代工厂库中提供的模拟I/Os为高速接口引入了过多的寄生电容。设计者要求ESD器件的总电容降低到15fF以下。

28nm CMOS SoC与硅光子器件共同封装在一个共享/混合集成封装中。该封装是在ESD受控环境下进行的。ESD防护等级降至200V HBM[7]。

28Gbps接口使用了差分对的概念。1V功能电路采用0.9V内核晶体管以保证开关速度。然而,这些晶体管将Rx、Tx信号的可用ESD设计窗口减少到4V。ESD保护的其他要求包括低漏电和小硅面积。

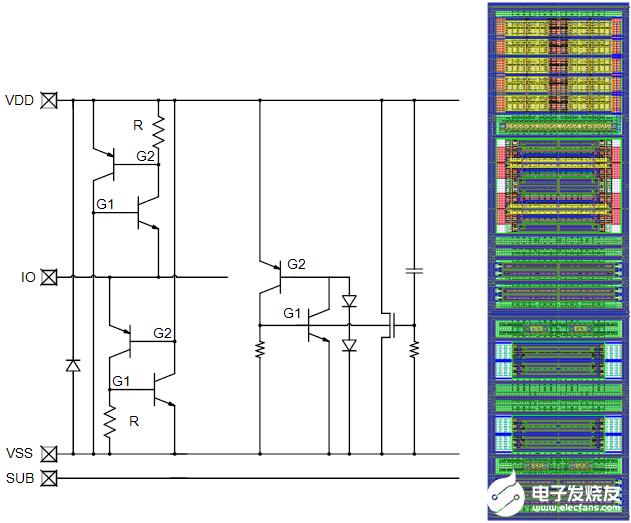

ESD保护设计包括一个完整的本地保护钳位概念,如下图所示。集成了一个1V电源钳,以确保所有应力情况都能在接口处进行本地处理,并消除了母线电阻的影响。整个钳位结构与基板隔离以减少来自衬底的噪音,这些噪音还可能来自芯片上与之较远的数字电路。

SerDes电路的Rx和Tx节点的完整本地保护方法的示意图(左)。 它基于Sofics专有的SCR ESD器件。 基于SCR的1V电源钳位集成在同一布局中(右)。 ESD的总面积为683.75um2。

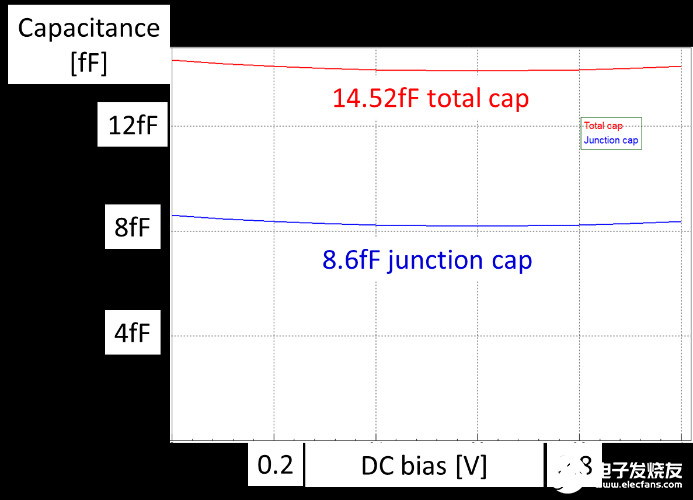

I/O PAD 上的总寄生电容来自不同方面。结电容可以很容易地从代工厂提供的二极管Spice模型中得出。与本地ESD钳位电路的金属连接会增加大量电容。寄生金属电容可以从PEX提取中得出。减小金属连接的宽度可以减小电容,但也会降低连接的稳健性。最小金属宽度是由我们通过对不同金属实施ESD应力得出的。当客户要求具有超低电容(远低于100fF)的ESD保护时,PEX提取中将包括Metal dummy部分(先进工艺中的CMP要求)。通过迭代(布局,PEX提取),ESD钳位电路的总寄生电容减小至小于15fF。下图显示了电容值与PAD上偏置电压的关系。

采用TSMC 28nm技术设计的完整本地ESD保护钳位的I / O电压两端的寄生电容(仅总电容和结电容)

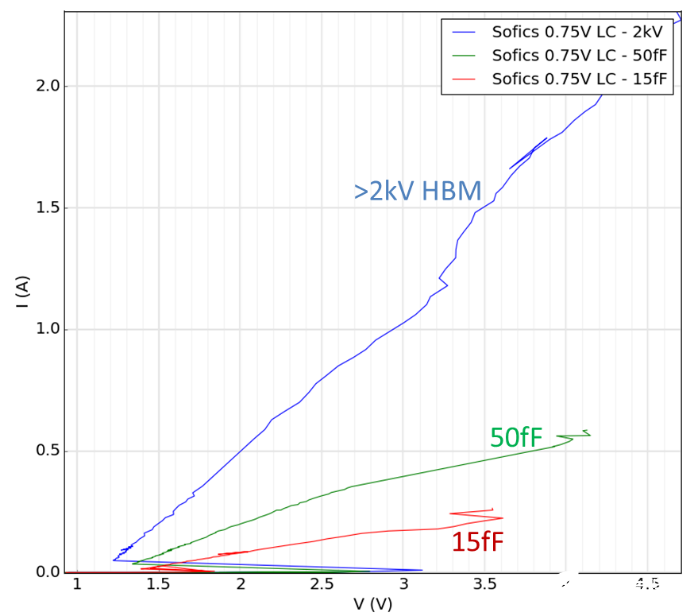

为了进一步增加光互连的带宽(超过56 Gbps),我们的客户采用了TSMC 7nm FinFET技术。我们提出的ESD解决方案与之前的方案相似。我们创建了两个版本的ESD保护方案,一个是50fF的寄生电容,另一个是小于15fF的版本。对台积电7nm FinFET工艺的测试表明,基于SCR的本地钳位性能符合预期。

在7nm技术中,内核晶体管(栅极到源极和漏极到源极)的故障电压约为3V。幸运的是,在许多SerDes应用中,由于其他晶体管串联在一起,所以有更多的余量。 根据电路原理,这些电路在ESD条件下的故障电压约为4-5V。

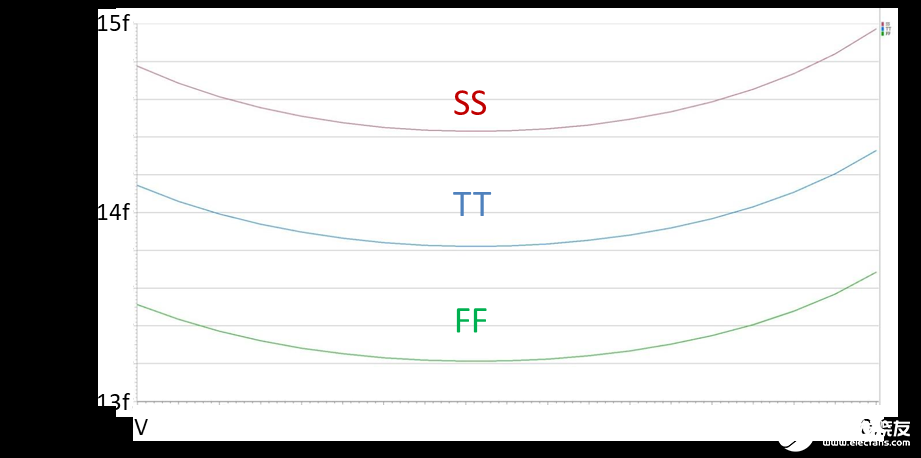

7nm低电容ESD钳位电路已集成到两个用于高速接口的设计中。对于15fF版本,典型、快速和慢速工艺角的IO电压上的仿真寄生电容如左图所示。它包括结电容(来自Spice模型)和金属化电容(基于PEX提取)。

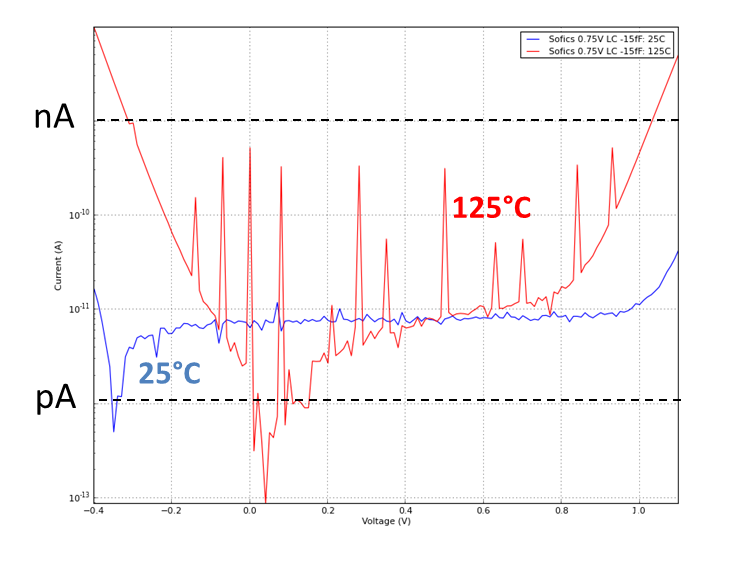

除了低寄生电容外,基于SCR的解决方案还具有低漏电流特性,比代工厂提出的ESD解决方案低几个数量级。 15fF版本的漏电测量如下所示。

在低温(25°C)和高温(125°C)下进行漏电流测量。 即使在高温下,ESD方案的漏电流在整个电压范围(0至0.75V)内也保持在1 nA以下。

硅光子技术可以促进(光学)通信市场的强劲增长。 借助光、电芯片的大规模生产机会以及2.5D和3D混合集成的可用性,可以满足市场的所有要求:更低的功耗,更低的成本,更大的容量,更高的带宽。

集成在硅光子产品中的高速SerDes接口需要以最小的寄生电容提供足够高的保护。在本文中,我们展示了用于28-56Gbps接口的TSMC 28nm和TSMC N7 FinFET的ESD保护钳位。在保证ESD鲁棒性的同时,实现了低于20fF的创纪录的低寄生电容水平。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。举报投诉

收发器芯片+光模块实现?或者是中间还需要电路进行转换?我知道Cyclone IV GX系列可以实现,但没有QFP封装的求明白人给解释一下,谢谢

的啊?求推荐网络芯片和资料,目前 想要 IP175G,但是找不到它的使用资料,外围电路搭接图,有知道的,请赐教!非常感谢~{:1:}

通讯,使用XILINX XAPP244的串行数据恢复功能感觉有些麻烦。使用XILINX的ROCKET I/O 实现150M的

我在官网上下载了CH569的数据手册和参考应用例程(EVT), 发现对SerDes这块的介绍很少, 而且EVT里也没有SerDes相关的例程.我想使用SerDes连接SFP模块来测试

之目的。要使光波成为携带信息的载体,必须对之进行调制,在接收端再把信息从光波中检测出来。然而,由于

的概况 1966年,美籍华人高锟(C.K.Kao)和霍克哈姆(C.A.Hockham)发表论文,预见了低损耗的

起源: 1966年,美籍华人高锟博士(C.K.Kao)和霍克哈姆(C.A.Hockham)

的优点有哪些? (1)智能弹窗,一天内站内弹窗不超过2次。(2)智能分页,长文章内容智能自动分页。(3)智能检测

作为一门新兴技术,是世界新技术的重要标志和未来信息社会中各种信息的主要传送工具。与传统

(Optical Fiber Communication)是以激光为光源,以光在一种特殊的光导纤维为传输介质进行传送信息的一种

技术发展综述. 中国科学: 信息科学, 2020, 50: 1361-1376 本文作者 余少华,何炜:中国信息

电源、参数匹配及业务倒换等方面的现状,分析存在的问题,并在此基础上提出解决问题的措施及思路。

im电竞官网平台